凯发k8娱乐官网|内参揭幕|芯片设计的两个板块:EDA和IP核

来源:凯发官网入口首页 发布时间:2024-05-20

d◈✿◈,制作图片要用Photoshop一样◈✿◈,它能高效设计◈✿◈、控制及管理数十亿电路元件在一颗芯片里协同工作◈✿◈。

而作为芯片设计核心之一的IP核◈✿◈:可谓是在芯片设计领域◈✿◈,其重要性不输芯片制造环节中的光刻机的存在◈✿◈。

lectual property core◈✿◈,中文名全称◈✿◈:知识产权核)◈✿◈;IP核是指芯片中具有独立功能的电路模块的成熟设计内参揭幕◈✿◈。早期◈✿◈,芯片的集成规模较小◈✿◈,设计复杂度不高◈✿◈,芯片上所有的电路都可以由芯片设计者自主完成◈✿◈;随着芯片集成度呈指数级增加◈✿◈,复杂性急剧增大◈✿◈,由一家企业独立完成一款复杂芯片的设计几乎变得不可能◈✿◈。 聪明的芯片工程师们想到了借鉴搭积木的思路◈✿◈:重复使用预先设计好的成熟构件◈✿◈,来搭建复杂系统◈✿◈,化繁为简◈✿◈,以求一键成“芯”◈✿◈。

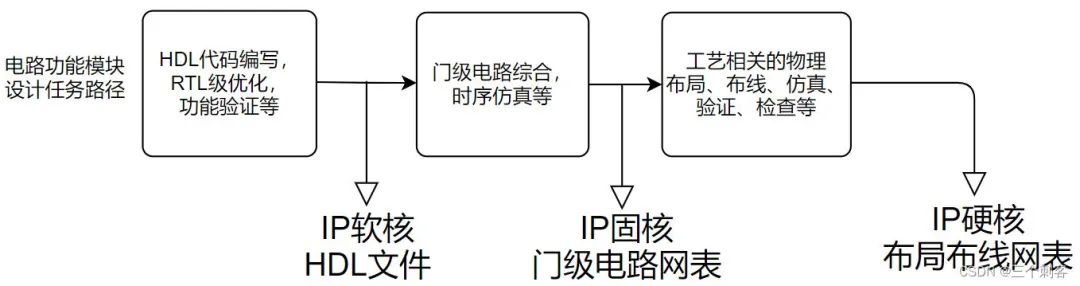

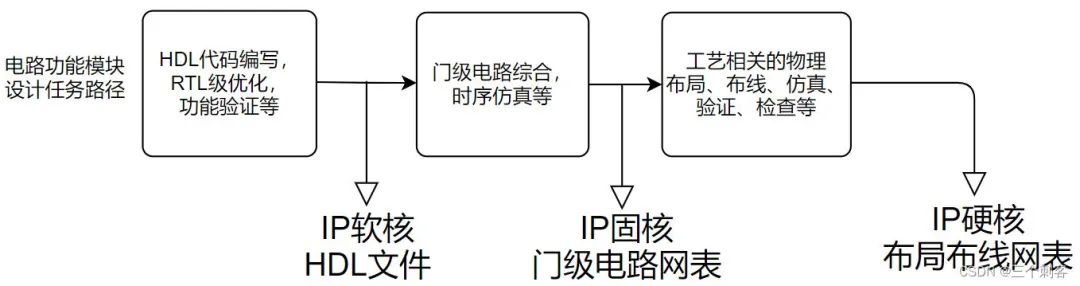

IP软核◈✿◈:是用Verilog/VHDL等硬件描述语言描述的功能块◈✿◈,如逻辑描述◈✿◈;它可沿用 Excel 的类比◈✿◈,IP 软核即为该图表模板的底层开发代码◈✿◈。

IP 固核◈✿◈:是以电路元件实现的功能模块◈✿◈。因为有一定的功耗约束◈✿◈、温度条件等◈✿◈,用户能够设置IP软核中的相应参数◈✿◈,将其转换成用逻辑门和触发器达成的电路◈✿◈,通常以门级电路网表的形式提供给客户◈✿◈。IP 固核可以看作是将底层代码中图表设置为部分固定的多个参数◈✿◈,并生成相应简单模板◈✿◈。

IP 硬核◈✿◈:与制造工艺相关(例如 CMOS 工艺)◈✿◈,完成了布局布线◈✿◈,提供电路设计的最终阶段产品—掩膜内参揭幕◈✿◈,进而进行光刻◈✿◈,生产芯片颗粒凯发k8娱乐官网◈✿◈。简单的理解IP硬核就是IP 硬核就是完全设定好的某一Excel图表模板◈✿◈,能够重复使用◈✿◈,能实现特定功能◈✿◈。

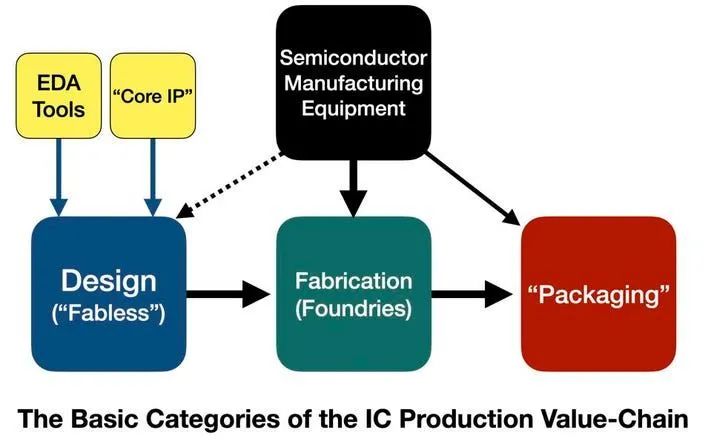

众所周知◈✿◈,半导体产业的发展经历了一个不断分工细化◈✿◈、上下游联动发展的过程◈✿◈;而◈✿◈,IP核的出现则让芯片设计和芯片代工从IDM模式中独立◈✿◈,成为芯片产业中的独立行业◈✿◈。

时至今日◈✿◈,无论是传统的芯片设计公司(Fabless)+芯片代工(FAB)模式◈✿◈,或是已经成为当今主流的芯片设计公司(Fabless)-材料设备-芯片代工(FAB)-封装公司-终端客户的模式中以IP核作为其核心竞争力的芯片设计公司的地位尤为凸显◈✿◈:

给这些设计公司提供架构和IP核的◈✿◈,则是Arm◈✿◈、Synopsys◈✿◈、Cadence等公司◈✿◈;其中Arm的市场占有率更是高达40%◈✿◈。

对于整个半导体产业链而言◈✿◈:IP核的出现及有效利用◈✿◈,势必会助力于半导体产业未来市场的正向增长◈✿◈:

IP核主要用于缩短芯片上市时间以及降低芯片开发成本◈✿◈,ARM的IP核生态可将芯片开发成本降低50%以上◈✿◈。

特别是对于它们而言◈✿◈:IP核的出现极大的降低了研发成本和研发风险◈✿◈,以风险共担◈✿◈、利益共享的模式形成了一个个小的以处理器内核为核心的生态圈◈✿◈,使得低成本创新成为可能◈✿◈。

并且在未来模块化设计趋势◈✿◈、产品协议迭代以及功能集成增加的推动下内参揭幕◈✿◈,IP需求将得到持续支撑◈✿◈,同时Chiplet 行业趋势亦有望为IP 行业带来新增量◈✿◈。

根据lPnest数据统计◈✿◈,在年均600多亿美元的全球芯片研发开支中◈✿◈,IP只占36亿美元◈✿◈,虽然占比只有5%◈✿◈,但从市场价值来看◈✿◈,IP的全球市场规模大约40亿美元◈✿◈,却带领着5000亿美元的半导体产业不断向前发展◈✿◈。

特别是相关的EDA厂商同为产业链上游玩家◈✿◈,其产品商业模式与IP 较为相似◈✿◈,且面对客户类型相同◈✿◈,故EDA 与IP 业务之间存在协同效应◈✿◈,EDA 公司切入IP 行业将具备天然优势◈✿◈。

综上所述◈✿◈,我们应该可以看出◈✿◈:我国未来想要走上半导体产业链的自主化道路◈✿◈,IP核的重要性丝毫不弱于光刻机◈✿◈!

国内代工厂以及芯片设计行业快速发展◈✿◈,芯片设计公司以及总销售额快速增长◈✿◈,也将推动对IP核的相应需求◈✿◈:

从行业下游领域来看◈✿◈:AI应用的拓宽◈✿◈,以及汽车智能化趋势需要新的IP 对产品进行适配◈✿◈,这也将产生额外的IP 需求◈✿◈,中国是AI 应用和汽车智能化的主要市场◈✿◈,国内企业有望借力下游领域快速发展◈✿◈,迎来发展良机内参揭幕◈✿◈。

同时◈✿◈,国内半导体行业的蓬勃发展带动了设计服务和芯片定制化行业发展◈✿◈,而设计服务等有业务又有望驱动国产IP 需求◈✿◈,部分国内IP 公司采用设计服务和IP 授权双轮驱动的发展战略◈✿◈。

当然◈✿◈,国产IP 发展离不开半导体产业生态的支持◈✿◈,近年来国内代工厂崛起◈✿◈,有望培育和带动国产IP 生态链的发展◈✿◈。

特别是对于被国内半导体产业链寄予厚望的Chiplet技术而言◈✿◈:国内IP核的自主研发无外乎是为Chiplet技术在拓宽“捷径”◈✿◈。

从这个意义上来说◈✿◈,Chiplet就是一个新的IP重用模式◈✿◈;未来内参揭幕◈✿◈,以Chiplet模式集成的芯片会是一个“超级”异构系统◈✿◈,可以带来更多的灵活性和新的机会◈✿◈。

与传统芯片设计方式相比◈✿◈,Chiplet具有迭代周期快◈✿◈,成本低◈✿◈,良率高等一系列优越特性◈✿◈。随着Chiplet技术的兴起◈✿◈,有望使芯片设计进一步简化为IP核堆积木式的组合内参揭幕◈✿◈,半导体制造链生态链可能会重构◈✿◈。

以计算芯片为例◈✿◈:Chiplet主要涉及计算◈✿◈、内存和IO接口◈✿◈,IO接口相对独立◈✿◈,计算最难和上层算法解耦◈✿◈,内存可以部分解耦◈✿◈;最终Chiplet会像搭乐高积木一样◈✿◈,通过取舍提高客户的迭代速度◈✿◈。

这将导致◈✿◈:一个Chiplet生态的第三方公司◈✿◈,直接从客户需求出发◈✿◈,“化繁为简”直接从设计到封装都可以直接帮客户定义◈✿◈。

声明◈✿◈:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载内参揭幕◈✿◈。文章观点仅代表作者本人◈✿◈,不代表电子发烧友网立场◈✿◈。文章及其配图仅供工程师学习之用◈✿◈,如有内容侵权或者其他违规问题◈✿◈,请联系本站处理◈✿◈。举报投诉

多且复杂凯发k8娱乐官网◈✿◈,即便是行业人士也无法熟悉每一个细分领域◈✿◈。 图片来源◈✿◈:中泰证券◈✿◈、平安证券 如上图所示◈✿◈,从整个

参数的模块,让其它用户可以直接调用这些模块,以避免重复劳动◈✿◈。随着CPLD/FPGA的规模越来越大,设计越来越复杂,使用

上JESD204B协议对应的引脚(SYSREF◈✿◈、SYNCINB和SERDOUT)与ZYNQ7015

◈✿◈:首先是系统设计对各个模块的时序要求很严格◈✿◈,不允许打乱已有的物理版图◈✿◈;其次是保护知识产权的要求◈✿◈,不允许设计人员对其有任何改动◈✿◈。

地址的具体原因是什么?这是与IPMI有关的吗?谢谢◈✿◈,以上来自于谷歌翻译以下为原文I have Intel NUC and I have manually assigned it a

版本太低◈✿◈,IPC部分不兼容了◈✿◈,但是查F28M35x Silicon Errata文档实在又查不出个所以然来◈✿◈。◈✿◈。◈✿◈。我把

中的某些模块(主要是scaler和interlacer)来实现高清图像转标清图像(具体就是1080p50转576i30

本帖最后由 ys_1*****8201 于 2016-5-19 14:16 编辑 Quartus

一次直至加满到15(4位计数器)后自动清零并开始下一轮计数◈✿◈。图5-14 二进制计数功能仿真波形假设现在想修改设计为8位计数器◈✿◈,当然可以再次修改

工程凯发k8娱乐官网◈✿◈,这个方法在之前的帖子中已经发过◈✿◈,不会的可以查看前面的相关帖子◈✿◈。创建好自己的工程◈✿◈:打开如下的菜单

一次直至加满到15(4位计数器)后自动清零并开始下一轮计数◈✿◈。图5-14 二进制计数功能仿真波形假设现在想修改设计为8位计数器◈✿◈,当然可以再次修改

◈✿◈,但是如何仿真呢?是用quartus自带软件◈✿◈,还是要用MATLAB?抑或其他?我用的自带软件◈✿◈,但是什么也没有出来◈✿◈。正确的办法应该怎样呢◈✿◈,谢谢指点◈✿◈。

地址(0000,0001)的输出数据不正确凯发k8娱乐官网◈✿◈,0002输出数据是地址0000对应的数据◈✿◈,即地址偏移了2位◈✿◈,请教给位大虾这是怎么回事?应该如何解决?

作Slave◈✿◈;下面的框图代表封装接口模块◈✿◈;从Master出来并进入Slave的箭头表示请求命令◈✿◈,从Slave出来并进入Master的箭头表示响应◈✿◈;加黑的线段代表片上互连总线◈✿◈。

大部分◈✿◈。其中硬件部分主要完成USB2.0协议中的链路层功能◈✿◈;而固件除协助硬件完成USB2.0

?具体问题是顶层仿真将如何知道XDC文件具有公共引脚位置参考但是针对不同的FPGA封装?即XDC是否具有特定于xdc文件唯一的包/ loc实例的信息?

ARM Cortex A9处理器◈✿◈,另一方面是FPGA(ZC7020)◈✿◈。我在FPGA端没有任何PCIe硬端口◈✿◈。因此

制造◈✿◈。(从技术上说◈✿◈,一种设计只有生产后才能实现◈✿◈。但是在此情况下◈✿◈,实现的意思是指安排布局并可直接投入生产)◈✿◈。SoC团队只需将硬核像一

软件◈✿◈,用VHDL硬件描述语言采用自顶向下的模块化设计方法◈✿◈,完成了具有相序自适应功能的双脉冲数字移相触发器的

封装接口模块◈✿◈;从Master出来并进入Slave的箭头表示请求命令◈✿◈,从Slave出来并进入Master的箭头表示响应◈✿◈;加黑的线段代表片上互连总线◈✿◈。

Netlist Writer”的时候出现这样的错误◈✿◈,Error: Cant generate netlist output files

ESP8266模块◈✿◈,通过无线路由器连接到远端的服务器上◈✿◈,可以随时向服务器发送数据◈✿◈;但是当服务器想要向这

计数器这个是counter模块:module counter ( cin, clock, cout, q

电平◈✿◈,控制总线暂停◈✿◈。 当主节点要求总线暂停时亦可采用同样的方法◈✿◈。图1是CPLD向外围I2C器件发送01010011 和01001001这

MAMF-011069集成双开关 - LNA 模块MAMF-011069 是一款双通道模块凯发k8娱乐官网◈✿◈,包含

再度走强◈✿◈,汇顶科技(603160)股价大涨7%◈✿◈,兆易创新(603986)以及上海新阳(300236)等个股也有不同程度的上涨◈✿◈。半导体◈✿◈,凯发官网入口首页◈✿◈,凯发天生赢家一触即发凯发k8·[中国]官方网站◈✿◈,天生赢家 一触即发◈✿◈。天生赢家·一触即发◈✿◈,k8凯发(中国)官方网站天生赢家·一触即发◈✿◈,